Researchers at Tohoku University, the University of Messina and the University of California, Santa Barbara (UCSB) have developed a scaled-up version of a probabilistic computer (p-computer) with stochastic spintronic devices that is suitable for hard computational problems like combinatorial optimization and machine learning.

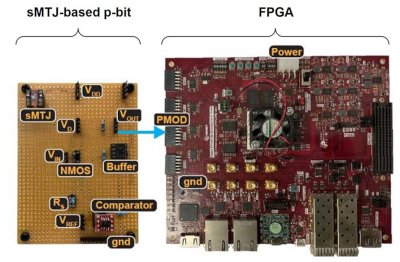

The constructed heterogeneous p-computer consisting of stochastic magnetic tunnel junction (sMTJ) based probabilistic bit (p-bit) and field-programmable gate array (FPGA). ©Kerem Camsari, Giovanni Finocchio, and Shunsuke Fukami et al.

A p-computer harnesses naturally stochastic building blocks called probabilistic bits (p-bits). Unlike bits in traditional computers, p-bits oscillate between states. A p-computer can operate at room-temperature and acts as a domain-specific computer for a wide variety of applications in machine learning and artificial intelligence. Just like quantum computers try to solve inherently quantum problems in quantum chemistry, p-computers attempt to tackle probabilistic algorithms, widely used for complicated computational problems in combinatorial optimization and sampling.

Recently, researchers from Tohoku University, Purdue University, and UCSB have shown that the p-bits can be efficiently realized using suitably modified spintronic devices called stochastic magnetic tunnel junctions (sMTJ). Until now, sMTJ-based p-bits have been implemented at small scale; and only spintronic p-computer proof-of-concepts for combinatorial optimization and machine learning have been demonstrated.

The research group recently presented two important advances.

First, they have shown how sMTJ-based p-bits can be combined with conventional and programmable semiconductor chips, namely, Field-Programmable-Gate-Arrays (FPGAs). The "sMTJ + FPGA" combination allows much larger networks of p-bits to be implemented in hardware, going beyond the earlier small-scale demonstrations.

Second, the probabilistic emulation of a quantum algorithm, simulated quantum annealing (SQA), has been performed in the heterogeneous "sMTJ + FPGA" p-computers with systematic evaluations for hard combinatorial optimization problems.

The researchers also benchmarked the performance of sMTJ-based p-computers with that of classical computing hardware, such as graphics processing units (GPUs) and Tensor Processing Units (TPUs). They showed that p-computers, utilizing a high-performance sMTJ previously demonstrated by a team from Tohoku University, can achieve massive improvements in throughput and power consumption than conventional technologies.

"Currently, the "s-MTJ + FPGA" p-computer is a prototype with discrete components," said Professor Shunsuke Fukami, who was part of the research group. "In the future, integrated p-computers that make use of semiconductor process-compatible magnetoresistive random access memory (MRAM) technologies may be possible, but this will require a co-design approach, with experts in materials, physics, circuit design and algorithms needing to be brought in."